# Numerical simulation and comparative assessment of DG-HEMT device for high-frequency application

Abdelmalik BELARBI<sup>1,a</sup>, Abdelkader HAMDOUNE<sup>2,b</sup>

<sup>1</sup>Department of Electrical and Electronic Engineering, Faculty of technology, Materials and Renewable Energy Research Unit, University of Abou-Bekr Belkaid, Tlemcen, Algeria <sup>2</sup>Professor, Department of Electrical and Electronic Engineering, Faculty of technology, Materials and Renewable Energy Research Unit, University of Abou-Bekr Belkaid, Tlemcen, Algeria

<sup>a</sup>belarbiabdelmalik@yahoo.fr, <sup>b</sup>ahamdoune@gmail.com

#### **Abstract:**

The main objective of this paper is to perform the DC and AC performances of GaN/InGaN/GaN Double Gate High Electron Mobility Transistor (DG-HEMT) based on innovative materials III-V in particular III-N materials (Nitride Materials) by using SILVACO TCAD device simulator. First, we modelled the structure with optimized physical and geometrical parameters. Secondly, we investigated the DC and AC performances; the device offers a maximum drain current of 1.6 A/mm, a threshold voltage of -2.2 V, a maximum transconductance of 0.8 S mm<sup>-1</sup>, a Ion/Ioff ration of 10<sup>10</sup>, a Drain Induced Barrier Lowering (DIBL) of 37 mV/V, a Sub-threshold Swing (SS) of 75 mV/dec and a Gate-leakage of 1.10<sup>-12</sup> A. In terms of AC performances, the device exhibits a cut-off frequency (Ft) of 990 GHz and a maximum oscillation frequency (Fmax) of 2 THz. Finally, a comparison study was carried out with a recent state of the art.

**Keywords:**GaN, InGaN, AlGaN, DG-HEMT, DC performances, AC performances.

#### 1. Introduction:

The III-V materials are promising and attractive compound semiconductors to develop high power with high frequency and very large scale integration circuits for next generation of RF applications such as high power amplifiers for space research, remote sensing, imaging systems and low noise wide bandwidth amplifiers design [1]. The high performances of recent electronic circuits are highly recommended for recent technology advances in digital and analog systems [2]. A dramatic performance in terms of frequency has been achieved [3-4]. In fact; III-V materials in particular III-N materials have a wide band gap energy and can potentially support a high breakdown voltage, also a high electron mobility serves to lead these components in the future to operate in high speed and low power computing [5].

The high electron mobility transistor based on III-V materials is a suitable device for terahertz frequency range [6] and the scaling down of the device's dimensions in order to minimize the transit time of careers and enhancing electrostatic integrity in the channel [7-8].

Scaling down the device's dimensions resulting an ultra short gate length; due to that, the device faces a severe undesirable effect such as short channel effect (SCE's) [8]. This effect heavily affects the DC and AC performances [9]. An appropriate parameter which is the aspect ratio needs to be maintained to minimize or suppress the short channel effect (SCE's) [10]. The aspect ratio represents the ratio of gate length and the distance from the gate electrode to the channel in the vertical direction [11].

The development of the technology leads to the use of double gate structure and the purpose is to mitigate the undesirable effects such as short channel affects (SCEs) so that can play a significant role to suppress the harmful effects on DC and AC performances [12-13]. The DG structure features of two gates electrodes deposited on the top and back sides; this architect structure provides an excellent electrostatic control of the device. Also; it contains two donor layers which serve to provide free electrons to the channel which improves the current density in the channel, another advantage is no buffer layer in this structure which means no substrate carrier injection. This results a dramatic enhancement of the performances and a better charge control of the device [14].

Our work consists to investigate the DC and AC performances of a DG-HEMT based on nitride materials, and to make a comparison with DG-HEMTs based on III-V materials obtained in state-of-the-art to demonstrate the importance of using innovative materials such as nitride alloys in these devices in microwave applications. It is organized according to the following parts: in the first section, the aim of our work is introduced. A second section is dedicated for the presentation of the simulated structure and different simulation models such as physical models and numerical method used also different physical and geometrical parameters. The third section contains the simulated DC and AC characteristics. Furthermore, a comparison study is carried out in order to validate our results and prove the importance of developing research through the use of III-V materials in particular III-N materials in these devices for high frequency and high power applications. Finally, a general conclusion is presented. The device performances are performed by using numerical simulation tools (SILVACO TCAD).

#### 2. Device structure and simulation models

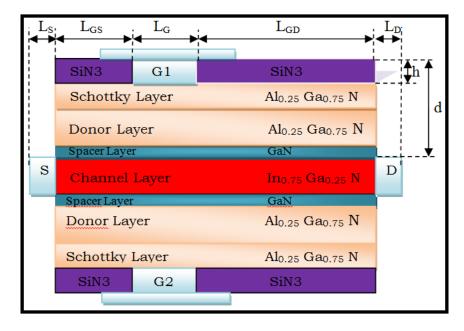

The schematic cross section of the simulated structure is shown in the Fig. 1. The device features the following physical and geometrical parameters: an undoped Schottky layer of  $Al_{0.25}Ga_{0.75}N$  and 1 nm of thick, a donor layer of  $Al_{0.25}Ga_{0.75}N$  with n-doping concentration of 3e19 cm<sup>-3</sup> and a thickness of 7 nm. An undoped spacer layer of GaN with 1 nm of thick is inserted between the donor and channel layers to separate the ionized donor atoms and the free electrons of the channel layer which furthermore improves the channel mobility; the channel layer is an undoped  $In_{0.75}Ga_{0.25}N$  with 10 nm of thickness.

The layers below the channel are identical to the one above the channel in order to form DG-HEMT structure. The gate length is fixed to 15 nm and the area of the device is 0.5  $\mu$ m  $\times$  200  $\mu$ m. The gate-source spacing (L<sub>GS</sub>) and the gate-drain spacing (L<sub>GD</sub>) are fixed to 110 nm and 370 nm, respectively. The table 1 shows the meaning of structure parameters.

Fig. 1: Schematic cross section of the simulated DG-HEMT.

Table. 1: Meaning of structure parameters.

| Structure parameters                                   | Value (nm) |

|--------------------------------------------------------|------------|

| Gate length (L <sub>G</sub> )                          | 15         |

| Spacing between gate to source side (L <sub>GS</sub> ) | 110        |

| Spacing between gate to drain side(L <sub>GD</sub> )   | 370        |

| Drain length in x direction (L <sub>D</sub> )          | 10         |

| Source length in x direction (L <sub>S</sub> )         | 10         |

| Thickness of SiN passivation layer (h)                 | 10         |

| Spacing between drain and top side (d)                 | 19         |

The simulation is performed in 2D with GUMMEL-NEWTON as numerical method to resolve Poisson and continuity equations. Taken from Silvaco ATLAS user's manuals [15], the physical models included in the simulation are the Shockley-Read-Hall (SRH) recombination mechanism to account the recombination effects, AUGER recombination to take accounts the high level injection effects, Bandgap Narrowing (BGN), and Parallel Electric Field (FLDMOB) to model the velocity saturation effect.

The physical parameters of the binary materials, GaN, AlN and InN are taken from Silvaco Atlas user's manual [15-16]; and the physical parameters of the ternary materials,

$In_{0.75}Ga_{0.25}N$  and  $Al_{0.25}Ga_{0.75}N$ , are deduced by linear interpolation according to the Vegard law [17].

## 3. Results and discussion DC performances

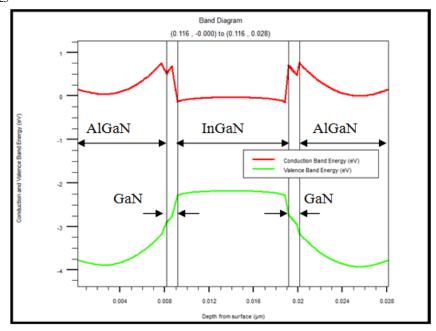

The Fig. 2 shows the energy band diagram, it presents the conduction and valence band energies as a function of depth from surface along the vertical direction of the device  $GaN/In_{0.75}Ga_{0.25}N/GaN$ .

Fig. 2: Energy band diagram of DG-HEMT.

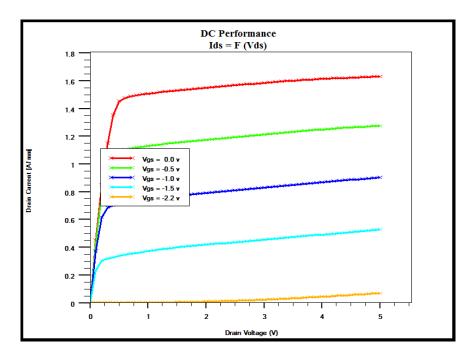

Fig. 3 shows the output characteristics: the drain-source current (Ids) as a function of drain-source voltage (Vds) for different gate-source voltages. The drain-source bias is swept from 0 V up to 5.0 V while the gate-source voltage is swept from 0 V to - 2.2 V. The maximum drain current obtained is 1.6A/mm at Vgs = 0.0V. This high saturated drain current is obtained with undoped channel and 10 nm of thickness, due to high electron density in the channel, and a knee voltage (Vknee) only of 0.5 V.

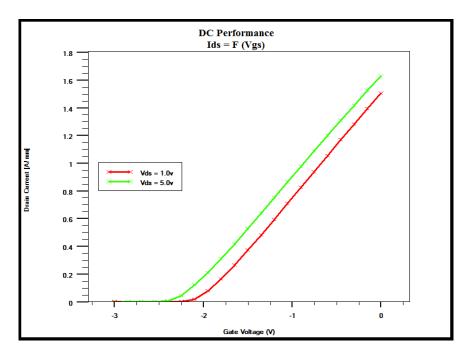

Fig. 4 shows the transfer characteristics: the drain-source current (Ids) as a function of gate-source voltage (Vgs) while the drain voltage is fixed at 1.0 V and 5.0 V, and the gate-source voltage was swept from 0.0 V to -3.3 V. The device presents a low threshold voltage due to an excellent control of the channel. The threshold voltages were about -2.1 V and -2.25 V for drain-source voltages (Vds) of 1.0 V and 5.0 V, respectively.

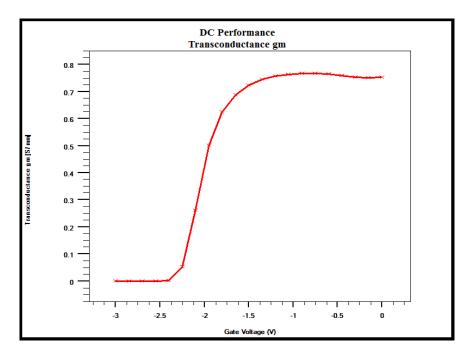

Fig. 5 shows the transconductance (gm) as a function of gate-source voltage (Vgs). The transconductance is the expression of the control mechanism of field effect transistors. Heterojunction Field Effect Transistors (HFETs) are characterized from all other FETs

devices by their high transconductance. The simulated device exhibits a maximum transconductance of 800 mS/mm at -1.0 V gate-source voltage while drain-source voltage is fixed at 1.0 V.

Fig. 3: The drain-source current as a function of drain source voltage while Vgs is swept from 0.0 V to -2.2 V, and Vds from 0.0 V to 5.0 V.

Fig. 4: The drain-source current (Ids) as a function of gate-source voltage (Vgs) while drain voltage is fixed at 1.0 V and 5.0 V, and gate-source voltage is swept from 0 V to -3.3 V.

The Drain Induced Barrier Lowering (DIBL) is an important parameter describing electrostatic integrity of The High Electron Mobility Transistor (HEMT). It is defined as the ratio of threshold voltage ( $V_{th}$ ) change to the drain-source voltage ( $V_{th}$ ) change ( $\Delta V_{th}$ ) (28]. In this work the DIBL is calculated at the difference between  $V_{th}$  for  $V_{ds1}$ =1.0v and  $V_{ds2}$ =5.0v. The DIBL is calculated by the equation (1).

DIBL = abs

$$\left[\frac{\Delta V \text{th}}{\Delta V \text{ds}}\right] = abs \left[\frac{V \text{th2} - V \text{th1}}{V \text{ds2} - V \text{ds1}}\right]$$

(1)

DIBL =  $abs \left[\frac{-2.25 - (-2.1)}{5 - 1}\right] = abs \left[\frac{-0.15}{4}\right] = 0.037 \ V/V$

DIBL = 37 mV/V

Where  $V_{th1} = -2.1v$  at Vds = 1.0v and  $V_{th2} = -2.25v$  at Vds = 5.0v

Fig. 5: Transconductance versus the gate-source voltage while drain-source bias is fixed at 1.0 V.

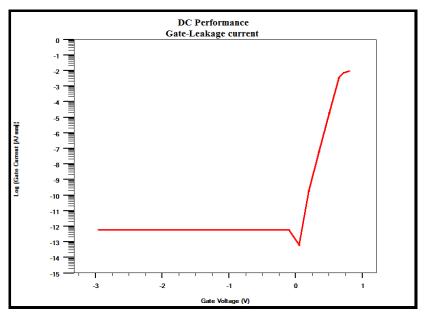

Fig. 6 shows the gate-leakage current as a function of gate-source voltage, while the drain bias is fixed at 1.0 V and the gate source is swept from 1.0 V to - 3.0 V for a DG-HEMT device based on nitride materials. The gate-leakage current is invariant with the gate bias, the device offers a gate leakage only of  $1.10^{-12}$  A at -3.0 V gate bias. This extremely low value is evident to indicate the high quality of the device.

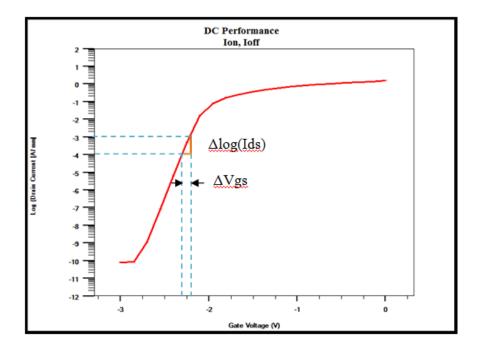

Fig. 7 shows the drain-source current plotted with log scale as a function of gate-source voltage. The On-state indicates the saturation current while the Off-state current is the sum of

total leakage current which includes sub-threshold, gate and junction leakage current [18]. The Ion/Ioff ratio extracted from the characteristics is about 10<sup>10</sup>. A high value of Ion/Ioff ratio is crucial parameter for power application. Furthermore, this parameter has an attractive attention on power consumption in static and standby power applications.

Fig. 6: Gate-leakage current as a function of gate-source voltage.

Fig. 7: Drain current plotted with log scale as a function of gate-source voltage.

The Sub-threshold Swing (SS) is determined on the log (Ids) characteristic as a function of Vgs. It corresponds to the gate-source voltage to be applied to reduce the drain current by one decade, it is defined in mV / dec. The SS is calculated by the equation (2).

Sub-threshold slope

$$\Longrightarrow$$

SS =  $\frac{\Delta Vgs}{\Delta \log{(Ids)}}$  (2)

$$SS = \Delta Vgs/dec$$

$$SS = Vgs2 - Vgs1/dec$$

$$SS = [-2.2125 - (-2.1375)] V/dec$$

$$SS = 0.075 V/dec$$

$$SS = 75 mV/dec$$

#### **AC** performance

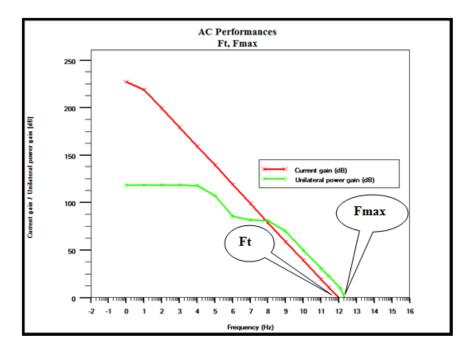

In this part, we perform the AC performances of the device by analyzing two important parameters: the cut-off frequency (ft) and the maximum oscillation frequency (fmax) [19]. The ft and fmax are evaluated when the current gain and the power unilateral gain are unities [20-21].

Fig. 8 shows the current gain and unilateral power gain as a function of the frequency, while the drain bias is fixed at 1.0 V and the gate bias is fixed at 0.0 V.

Fig. 8: The current gain and the unilateral power gain as a function of the frequency, while the drain bias is fixed at 1.0 V, and the gate bias is fixed at 0.0 V.

For a gate length of 15 nm, the device exhibits a cut-off frequency of 990 GHz and a maximum oscillation frequency of 2 THz, while the drain-source voltage is fixed at 1.0 V. The device exhibits excellent AC performances compared to the results found in the state of the art.

The results found are very impressive and attractive for power applications and terahertz range; the reason is the use of particular nitride materials, and the source and drain electrodes

are in direct contact with the channel layer. In a conventional structure, these electrodes are far from the channel layer, and would give lower RF performance.

The table 2 contains the device's characteristics and the table 3 and 4 presents a comparison of our results such as the cut-off frequency (Ft), the maximum oscillation frequency (Fmax) and digital characteristics with the highest values reported in the state of the art.

Table 2: Device characteristic of the simulated DG-HEMT.

V

| Device's characteristics of DG-HEMT with gate length of 15nm | Results             |

|--------------------------------------------------------------|---------------------|

| Drain current I <sub>D</sub> ( A/mm)                         | 1.6                 |

| Threshold voltage Vth ( V )                                  | -2.2                |

| Transconductance gm ( S/mm )                                 | 0.8                 |

| Drain Induced Barrier Lowring DIBL ( mV/V )                  | 37                  |

| Sub-threshold Swing SS ( mV/dec )                            | 75                  |

| Gate-leakage current ( A )                                   | 1.10 <sup>-12</sup> |

| Ion/Ioff ratio                                               | $1.10^{10}$         |

| Cut-off frequency Ft (Ghz)                                   | 990                 |

| Maximum oscillation frequency Fmax (Ghz)                     | 2000                |

Table 3: Comparison of highest reported Ft and Fmax in the state of the art based on III-materials with our reported DG-HEMT based on III-N materials (Nitride materials).

| Reference | Gate length (nm) | Ft (Ghz) | Fmax (Ghz) | Year |

|-----------|------------------|----------|------------|------|

| [22]      | 100              | 192      | 288        | 2004 |

| [23]      | 100              | -        | 257        | 2006 |

| [24]      | 50-100           | 258-214  | 286-287    | 2007 |

| [25]      | 50               | 175      | 448        | 2013 |

Note: Accepted manuscripts are articles that have been peer-reviewed and accepted for publication by the Editorial Board. These articles have not yet been copyedited and/or formatted in the journal house style.

| This work | 15    | 990     | 2000     | 2018 |

|-----------|-------|---------|----------|------|

| [8]       | 30    | 809     | 1030     | 2018 |

| [27]      | 30-50 | 825-710 | 1082-989 | 2017 |

| [26]      | 30    | 776     | 905      | 2017 |

Table 4: Comparison of highest reported DC performances in the state of the art based on III-V materials with our reported DG-HEMT based on III-N materials (Nitride materials).

| Reference    | $L_{G}$ | $I_D$  | V <sub>th</sub> | Gate-               | gm     | $I_{on}/I_{off}$   | DIBL | SS | Year |

|--------------|---------|--------|-----------------|---------------------|--------|--------------------|------|----|------|

|              | (nm)    | (A/mm) | (V)             | leakage (A)         | (S/mm) |                    |      |    |      |

| [22]         | 100     | 0.6    | -0.4            | -                   | 2.8    | -                  | -    | -  | 2004 |

| [23]         | 100     | 0.82   |                 | -                   | 2.3    | -                  | -    | -  | 2006 |

| [24]         | 100     | 0.56   | -0.4            | -                   | 2.6    | -                  | 15   | 75 | 2007 |

| [25]         | 50      | -      | -               | -                   | 1.81   | -                  | -    | -  | 2013 |

| [26]         | 30      | 0.98   | 0.29            | 1                   | 3.09   | $2.24 \times 10^5$ | 68   | 73 | 2017 |

| [27]         | 50      | 1.42   | 0.26            | 1                   | 3.58   | -                  | 58   | 62 | 2017 |

| [8]          | 30      | 1.2    | 0.21            | -                   | 3.3    | -                  | -    | -  | 2018 |

| This<br>work | 15      | 1.6    | -2.1            | 1.10 <sup>-12</sup> | 0.8    | 1.10 <sup>10</sup> | 37   | 75 | 2018 |

#### **Conclusion**:

In summary, we have investigated the DC and AC performances of a DG-HEMT based on III-V materials in particular nitride materials (III-N) by using two dimensional TCAD simulator (SILVACO TCAD). The use of two gates on both sides of the device provides a

significant improve in its performances which become very dominant in high power and high field conditions. The better channel control with double gate (DG) has been achieved by suppressing the undesirable effect such as short channel effect (SCE) in terms of DIBL and SS. The device exhibits a maximum drain current of 1.6 A/mm, a threshold voltage of -2.2 V, a maximum transconductance of 800 mS mm<sup>-1</sup>, an Ion/Ioff ratio of 10<sup>-10</sup>, a Drain Induced Barrier Lowering (DIBL) of 37 mV/V, a Sub-threshold Swing (SS) of 75 mV/dec, and a Gate-leakage current of 1.10<sup>-12</sup> A. Furthermore, a dramatic AC performance in terms of cut-off frequency (Ft) and maximum oscillation frequency (Fmax) has been achieved. A comparison study was carried out with a recent state of the art and the obtained results provide a reference for future research to use III-V materials in particular nitride materials (III-N) for power applications and terahertz range.

#### Acknowledgments

This work was supported by the Materials and Renewable Energy Research Unit of the University of Tlemcen (Algeria). The author wishes to thank the professor A. Hamdoune for his support.

#### References

- [1] P.Murugapandiyan , S.Ravimaran , J.William, , "DC and microwave characteristics of AlN spacer based  $Al_{0.37}Ga_{0.63}$  N /GaN HEMT on SiC substrates for high power RF applications," Int. J. Nanoelectronics and Materials , vol. 10, pp. 111-122, 2017

- [2] Subhra Chowdhury, Dhrubes Biswas, "Effect of device parameters on transmission coefficient of Al<sub>0.2</sub> Ga<sub>0.8</sub> N/GaN ResonantTunning Diode grown on silicon substrate," Int. J. Nanoelectronics and Materials, vol.**6**, pp. 129-137, 2013

- [3] Zafar.S, "Designing of double gate HEMT in TCAD for THz applications," in: Proceedings of 2013 10th International Bhurban Conference on Applied Sciences and Technology (IBCAST), pp.402–405, 2013.

- [4] Wang. L, "Modeling the back gate effects of AlGaN/GaN HEMTs," J. Comput. Electron. **13**(4), 872–876, 2014

- [5] kim, D.H, "Performance evaluation of 50 nm In<sub>0.7</sub> Ga<sub>0.3</sub> As HEMTs for beyond-CMOS logic applications," IEEE International Electron Devices meeting. IEDM Technical Digest, pp. 767–770, 2005.

- [6] Zafar S, Kashif A, Hussain S, Akhtar N, Bhatti N, Imran M, "Designing of double gate HEMT in TCAD for THz applications," in 10th International Bhurban conference on applied sciences & technology (IBCAST), 2013 Jan 15–19, Islamabad, Pakistan: IEEE Xplore p. 402–5, 2013.

- [7] Kim DH, Del Alamo JA. Scalability of sub-100 nm thin-channel InAs PHEMTs. In: Proceedings of the IEEE international conference on indium phosphide & related material, 2009 May 10–14, Newport Beach, CA, USA. IEEE Xplore, pp. 132–5, 2009.

- [8] Saravana Kumar Radhakrishnan, Baskaran Subramaniyan, Mohanbabu Anandan, Mohankumar Nagarajan. Comparative assessment of InGaAs sub-channel and InAs composite channel double gate (DG)-HEMT for sub-millimeter wave applications. Int. J. Electron. Commun. (AEÜ) 83, pp. 462–469, 2018

- [9] Kim, D.H, "Lateral and vertical scaling of In<sub>0.7</sub> Ga<sub>0.3</sub> As HEMTs for post-Si-CMOS logic applications," IEEE Trans. Electron Devices. **55**(10), pp 2546–2553, 2008.

- [10] Gomes, U.P, Impact of aspect ratio on the logic performance of strained In0.53Ga0.47As metamorphic HEMT. J. Electron Devices, vol. **13**, 939–944, 2012.

- [11] Vasallo, B.G, "Comparison between the dynamic performance of double- and single-gate AlInAs/InGaAs HEMTs," IEEE Trans. Electron Devices **54**(11), pp 2815–2822, 2007.

- [12] Vasallo, B.G., Wichmann, N., Bollaert, S., & Roelens, Y., "Comparison Between the Dynamic Performance of Double- and Single-Gate AlInAs/InGaAs HEMTs," IEEE Trans. on Electron. Devices, vol. 54-11, pp. 2815-2822, 2007.

- [13] Rathi, S., Jogi, J., Gupta, M., & Gupta, R.S., "Modeling of heterointerface potential and threshold voltage for tied and separate nanoscale InAlAs–InGaAs symmetric doublegate HEMT," Microelectronics Reliability, vol. 49, pp 1508–1514, 2009.

- [14] Vasallo BG, Wichmann N, Bollaert S, Roelens Y., "Comparison between the dynamic performance of double- and single-gate AlInAs/InGaAs HEMTs," IEEE Trans. Electron. Devices, vol. 54-11, pp. 2815–22, 2007.

- [15] ATLAS user's manual www.silvaco.com, chapter 2: defining material parameters, models and choosing numerical methods, 2004, pp. 27-38.

- [16] Ougazzaden A, Gautier S, Moudakir T, Djebbour Z, Lochner Z, Choi S, KimHJ, Ryou JH, Dupuis RDand Sirenko AA, "Band gap bowing in BGaN thin films, " Appl. Phys. Lett. 93 083118, 2008.

- [17] Lachebi A, Abid H, DrizMand Al-Douri Y, "First-principles study of cubic B<sub>x</sub> Ga<sub>1-x</sub> N alloys " Int. J. Nanoelectron. Mat, vol. 1, pp. 81–90, 2008.

- [18] Pardeshi, H.M., Raj, G., Pati, S., Kumar, N. M., & Sarkar, C.K, "Performance assessment of gate material engineered AlInN/GaN underlap DG MOSFET for enhanced carrier transport efficiency," Superlattices and Microstructures, vol. 60, pp. 10–22, 2013.

- [19] Hayati M, Akhlaghi B, "An extraction technique for small signal intrinsic parameters of HEMTs based on artificial neural network, " Int J Electron Commun 67:123–9, (AEÜ) 2013.

- [20] Mohankumar N, Syamal B, Sarkar CK, "Influence of channel and gate engineering on the analog and RF performance of DG MOSFETs," IEEE Trans. Electron. Devices, vol. 57-4, 820-6, 2010.

- [21] Murugapandiyan P, Ravimaran S, William J, "DC and microwave characteristics of Lg 50nm T-Gate InAlN/AlN/GaN HEMT for future high power RF applications," Int J Electron Commun (AEÜ), 77:163–8. 2017.

- [22] N. Wichmann, I. Duszyns, S. Bollaert, J. Mateos, X. Wallad, A. Gappy, "IOOnm InAIAs/InGaAs Double-Gate HEMT using transferred substrate," IEEE, pp. 41,2,1-41,2,4. 2004.

- [23] B. G. Vasallo, N. Wichmann, S. Bollaert, A. Cappy, T. Gonzalez, D. Pardo and J. Mateos. "Monte Carlo Comparison Between InP-Based Double-Gate and Standard HEMTs," Proceedings of the 1st European Microwave Integrated Circuits Conference, pp. 304-307, Manchester UK. September 2006.

- [24] Beatriz G. Vasallo, Nicolas Wichmann, Sylvain Bollaert, Yannick Roelens, Alain Cappy, Senior Member, IEEE, Tomás González, Senior Member, IEEE, Daniel Pardo, and Javier Mateos, "Comparison Between the Dynamic Performance of Double- and Single-Gate AlInAs/InGaAs HEMTs," IEEE Trans. on electron. devices, vol. 54, NO. 11, pp. 2815-2822, November 2007.

- [25] S. Zafar a. b, A. Kashifa, S. Hussain b, N. Akhtar a, N. Bhatti a and M. Imran a, "Designing of Double Gate HEMT in TCAD for THz Applications," Proceedings of 2013 10th International Bhurban Conference on Applied Sciences & Technology (IBCAST) Islamabad, Pakistan, 15th 19th Jan. 2013.

- [26] Saravana Kumar R, Mohanbabu A, Mohankumar N & Godwin Raj D, "Simulation of InGaAs Sub-channel DG-HEMTs for analog / RF applications," International Journal of Electronics, pp. 1-21. Sep. 2017.

- [27] SaravanaKumar R, Mohanbabu A, Mohankumar N, Godwin Raj D, "In<sub>0.7</sub> Ga<sub>0.3</sub> As/In<sub>0.7</sub> Ga<sub>0.3</sub> As composite-channel double-gate (DG)-HEMT devices for high frequency applications," J Comput Electron, 16. 10.1007/s10825-017-0991-x, 2017.

- [28] Park, P.S, "Simulation of short-channel effects in N- and Ga-polar AlGaN/GaN HEMTs," IEEE Trans. Electron Devices vol. 58, No.3, pp. 704–708, (2011)