# A Simplified Surface Potential Based Current Model for Gate-All-Around Carbon Nanotube Field Effect Transistor (GAA-CNFET)

Ankita Dixit and Navneet Gupta\*

Department of Electrical and Electronics Engineering, Birla Institute of Technology and Science, Pilani, Rajasthan, 333031, India.

Received 8 February 2021, Revised 18 March 2021, Accepted 25 March 2021

### ABSTRACT

This paper presents a simple surface-potential based drain current  $(I_d)$  model for gate-allaround carbon nanotube field effect transistor (GAA-CNFET). The model captures a number of features which include ballistic transport, first subband minima, chirality and non-existence of fringing and screening effect due to its geometry. Further, the effect of chirality on subthreshold swing (SS), current on/off ratio ( $I_{ON/OFF}$ ) and transconductance ( $g_m$ ) is studied by extracting these parameters from drain current variation. It is observed that there exists a trade-off between the parameters for different chiral vector CNTs. As chirality increases, transconductance and subthreshold slope increases while current on/off ratio reduces. To confirm the validity of proposed model, virtually fabricated GAA-CNFET device performance was simulated and compared with the calculated values. The variation is also compared with the experimental result of actually fabricated device. The close match between calculated, simulated and experimental results confirms the validity of the proposed model.

**Keywords:** Carbon nanotube, carbon nanotube field effect transistor (CNFET), chirality, device modeling, Subband

## 1. INTRODUCTION

Carbon nanotube field effect transistor (CNFET) is considered as one of the preferable candidates to complement silicon (Si)-based metal-oxide semiconductor (MOS) devices [1-3]. One of the key factors that restrict further scaling of Si MOS devices is the short channel effects (SCE), which degrades the performance of the device in terms of high power consumption during turning off the device [4-6]. The advantages of carbon nanotubes (CNTs) include energy-efficient computation because of their high carrier velocity and near-ballistic carrier transport property [7-9]. Moreover, due to very thin structure of CNT, the gate control of the CNFETs is superior and this makes it capable to overcome the SCE even in the sub-10 nm technology node [10-11]. In recent years, a lot of advancement has taken by various research groups [12-16] and addressed key challenges in the CNFET technology.

In order to understand the performance of CNFET, it is utmost important to study the performance of the fabricate device based on the optimisation obtained using simulation results. However, it is also important to assess the results and understand the physics behind transport mechanism based on an analytical model. Various approaches have been used for

<sup>\*</sup> Corresponding Author: ngupta@pilani.bits-pilani.ac.in

analysing the performance of CNFET. Some extensively employed methods include; Nonequilibrium Green's function (NEGF) formalism, Landauer formula [17-18], virtual source approach and optimized geometry approach [11-12, 19]. However, these methods are computationally expensive, have limited scope and based on parameter extraction.

In this paper, a simplified model for gate-all-around CNFET (GAA-CNFET) is proposed which is based on the dependency of current on the surface potential of CNT. The main features of this model include:

- (i) The model is based on the ballistic transport of charge carriers in channel.

- (ii) Screening and fringing effects are neglected as GAA structure is free from sharp edges.

- (iii) The effect of chirality of CNT on the performance of the device.

- (iv) The model has been verified against the simulated results and published experimental data.

This paper is organised as follows: analytical expressions, theory behind the development of this model and parameter extraction are described in Section 2. Section 3 explains the results and discussion obtained from analytical model and simulations. It also describes the effect of chirality on drain current ( $I_d$ ) and finally the conclusion of this study is given in section 4.

## 2. THEORY AND MODEL

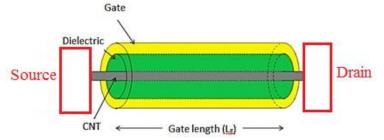

To understand the working of CNFET, many approaches have been used. J. luo et al. [19] proposed a compact model for multichannel CNFET. This model has semiempirical approach for CNFET. The screening effect is considered for modelling due to multichannel CNT. C-S Lee et al. [11] presented a data calibrated model which is based on virtual source approach. A. Deyasi et al. [27] described a current model for CNFET using NEGF approach. They have analysed drain current, subthreshold swing and quantum capacitance for GAA-CNFET, however this method is computationally expensive. In the proposed model, screening and fringing effects are neglected due to GAA structure with single wall CNT in channel. The performance of CNFET is mainly dependent upon I<sub>d</sub> which is controlled by gate. The effectiveness of gate control further depends on various other parameters which include; type of gate dielectric material, chirality and diameter of CNT [28]. Other electrical parameters which effect the device performance are gateto-source voltage ( $V_{gs}$ ) and drain-to-source voltage ( $V_{ds}$ ). For the choice of gate dielectric material, a systematic study was performed to select the best possible gate material for GAA-CNFET. It was found that lanthanum oxide (La<sub>2</sub>O<sub>3</sub>) and hafnium oxide (HfO<sub>2</sub>) are the best gate dielectric material to be used for GAA-CNFET [20]. In order to compare our result with that of experimental one, it was assumed that gate dielectric is made up of HfO<sub>2</sub> and the structure considered for GAA-CNFET is shown in Figure 1.

Figure1. Gate-all-around CNFET device structure used in current model.

The procedure used for computing the  $I_d$  includes the consideration of the energy of each subband and the associated probability of occupation in these subbands. The intrinsic CNT contains two types of charge carriers, one with positive velocities and other with negative velocities, hence the total  $I_d$  in channel can be written as:

$$I_d = \frac{2q}{h} \times \left[ \int F(E, E_F - qV_{gs}) - \int F(E, E_F - qV_{ds}) \right] dE$$

<sup>(1)</sup>

where *h* is Planck's constant, *F*() is the Fermi function,  $E_F - qV_{gs}$  and  $E_F - qV_{ds}$  are the Fermi levels in the source and drain contacts, respectively. Considering zero source voltage and integrating from energy level  $E_{cb}$  -  $qV_{CNT}$  to infinity, we can represent Eq. (1) as:

$$I_{d} = \frac{2q}{h} \times \int_{E_{cb}}^{\infty} \left[ F(E, E_{F} - qV_{g}) - F(E, E_{F} - qV_{d}) \right] dE$$

<sup>(2)</sup>

The degeneracy occurs due to two or more than two subbands having same energy level, therefore the additional factor of 2 is included in Eq. (2), hence solving Eq. (2) gives:

$$I_{d} = \frac{4qkT}{h} \times \left[ \ln\left\{ 1 + \exp\left(\frac{qV_{CNT} - qV_{g} - \Delta_{1}}{kT}\right) \right\} - \ln\left\{ 1 + \exp\left(\frac{qV_{CNT} - qV_{d} - \Delta_{1}}{kT}\right) \right\} \right]$$

(3)

where,  $V_{CNT}$  is the surface potential and  $\Delta_1$  is the first subband minima.  $V_{CNT}$  can be represented by following empirical relationship [21]:

$$V_{CNT} = \begin{cases} V_g & \text{for } V_g < \Delta_1 \\ V_g + \alpha (V_g - \Delta_1) & \text{for } V_g > \Delta_1 \end{cases}$$

(4)

where,  $\Delta_1 = \frac{E_g}{2q}$  (first subband minima) and  $\alpha$  is the slope of the curve which is calculated by following equation [22]:

$$\alpha = \alpha_0 + \alpha_1 V_g + \alpha_2 V_g^2 \tag{5}$$

where  $\alpha_0$ ,  $\alpha_1$  and  $\alpha_2$  are empirical parameters which can be calculated by matrix method:

| $\begin{bmatrix} \alpha \\ \end{bmatrix} \begin{bmatrix} 1 & V \end{bmatrix}$ | $V_g V_g^2 \left[ \alpha_0 \right]$                                                                                                                                                      |     |

|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| $\left  \alpha \right  = \left  1 \right  V$                                  | $V_g V_g^{"2} \left\  \begin{array}{c} \alpha_1 \\ \alpha_1 \end{array} \right\ $                                                                                                        |     |

| $\alpha^{"'}$ 1 V                                                             | $\begin{bmatrix} v_{g} & v_{g}^{2} \\ v_{g}^{*} & v_{g}^{*2} \\ v_{g}^{*} & v_{g}^{*2} \end{bmatrix} \begin{bmatrix} \alpha_{0} \\ \alpha_{1} \\ \alpha_{1} \\ \alpha_{2} \end{bmatrix}$ |     |

|                                                                               |                                                                                                                                                                                          | (6) |

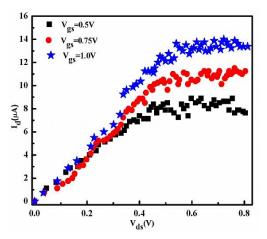

In order to calculate  $\alpha_0$ ,  $\alpha_1$  and  $\alpha_2$ , we analysed the behaviour of GAA-CNFET for various gate voltages (V<sub>g</sub>). Though the values of these empirical parameters are available for planar structure [21], we have calculated these parameters for GAA structure by using the output characteristics of GAA-CNFET. Figure 2 shows the output characteristic of GAA-CNFET for 30 nm channel length [23]. The empirical parameters  $\alpha'$ ,  $\alpha''$  and  $\alpha'''$  in Eq. (6) are the slope of drain current corresponding to V<sub>g</sub> of 0.5 V, 0.75 V and 1.0 V, respectively. The value of  $\alpha_0$ ,  $\alpha_1$  and  $\alpha_2$  obtained are 1, -0.05625 V<sup>-1</sup> and 1.175 V<sup>-2</sup>, respectively.

Figure 2. Experimental Id-Vds characteristics of GAA-CNFET. Experimental results of [23].

The first subband minima is the half of the energy band gap, therefore Eq. (3) can be rewritten as:

$$I_{d} = \frac{4qkT}{h} \times \left[ \ln \left\{ \frac{1 + \exp\left(\frac{qV_{CNT} - qV_g - \Delta_1}{kT}\right)}{1 + \exp\left(\frac{qV_{CNT} - qV_d - \Delta_1}{kT}\right)} \right\} \right]$$

(7)

So, the final drain current equation obtained depends on surface potential of CNT, chirality of CNT, gate voltage and drain voltage.

### 3. RESULTS AND DISCUSSION

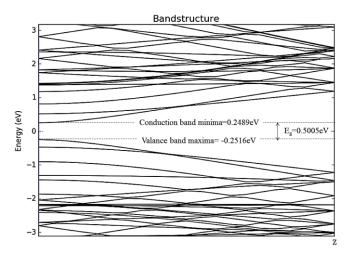

In order to analyse the performance of GAA-CNFET, CNT (19, 0) has been considered because the diameter of this CNT is 1.49 nm which is same as that of the CNT diameter of fabricated GAA-CNFET. The I<sub>d</sub> has been calculated using Eq. (7) and compare it with fabricated result. In order to use the value of  $\Delta_1$ , we need the energy band gap (E<sub>g</sub>) of CNT (19, 0). For this, we analysed the energy band diagram of CNT (19, 0) using Atomistic QuantumATK tool. Figure 3 shows the band structure of CNT (19, 0) which gives the energy band gap (E<sub>g</sub>) of 0.5005 eV. The conduction minima and valance band maxima are 0.2489 eV and -0.2516 eV, respectively.

Figure 3. Energy band structure for CNT (19, 0)

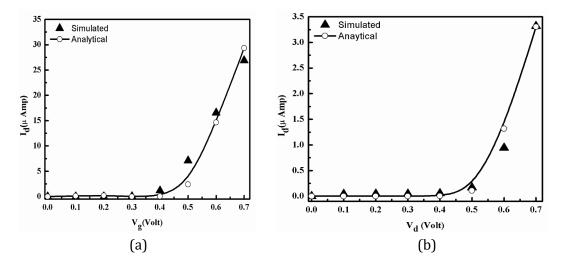

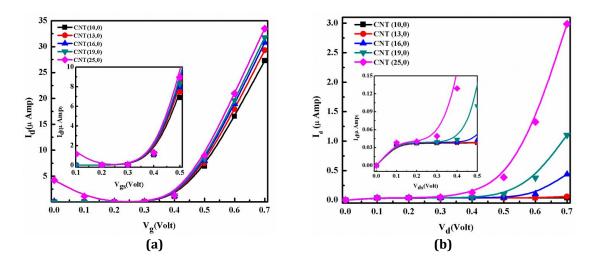

In order to confirm the validity of the current model, GAA-CNFET is virtually fabricated and its performance was analysed using Technology Computer-aided Design (TCAD) simulator. Figure 4 shows the transfer and output characteristics plotted using analytical model and using simulation. It is observed from Figure 4 (a), that as  $V_g$  increases beyond 0.4 V, there is a steep rise in the drain current. This is attributed from the fact that minimum 0.4 V is required for the carrier to overcome the potential barrier at the channel end. This trend shows the excellent match for the calculated value of drain current and the simulated results. Figure 4 (b) shows the output characteristic of GAA-CNFET. It is observed that analytical values are approximately same as the simulated result. The solid lines in Figure 4 are the best fitting curve of calculated values based on analytical model.

**Figure 4.** Comparison between the calculated and simulated (a) transfer and (b) output characteristics of GAA-CNFET at V<sub>d</sub> and V<sub>g</sub> of 0.3 V, respectively.

Chirality (n, m) of CNT depends on its diameter and hence on its energy band gap which further also affects surface potential of CNT (V<sub>CNT</sub>). This indicate that the I<sub>d</sub> of CNFET will also depend on the chirality (n, m) of CNT. The diameter (d) and energy band gap (E<sub>g</sub>) of CNT are given by [24]:

$$d = \frac{\sqrt{3}a_{c-c}}{\pi}\sqrt{n^2 + nm + m^2}$$

163

(8)

and

$$E_{g} = \frac{2a_{c-c}t}{d} = \frac{0.852}{d(nm)}(eV)$$

(9)

where, *t* is the nearest-neighbour hopping parameter and  $a_{c-c}$  is the carbon-carbon bond length. Table 1 shows the calculated and simulated values of diameter and energy band gap of zigzag type CNT (n,0) [26]. A folded graphene sheet along with one of two chiral vectors at chiral angle of 0° angle defines as zigzag CNT (n, 0). It is observed that as chirality increases, diameter of CNT increases but its energy band gap decreases. This inverse proportional trend of bandgap of CNT with its diameter is also observed from Kataura plot [25]. It is also observed that diameter and energy band gap values from simulation and calculation are close to each other.

| CNT     | Diameter (nm) |           | Energy Band Gap (eV) |           |

|---------|---------------|-----------|----------------------|-----------|

| CNT     | Calculated    | Simulated | Calculated           | Simulated |

| (10, 0) | 0.7830        | 0.7829    | 1.0880               | 1.0534    |

| (13, 0) | 1.0179        | 1.0178    | 0.8369               | 0.8178    |

| (16, 0) | 1.2528        | 1.2526    | 0.6800               | 0.6668    |

| (19, 0) | 1.4877        | 1.4875    | 0.5726               | 0.5633    |

| (25, 0) | 1.9576        | 1.9572    | 0.4352               | 0.4299    |

#### Table 1 Diameter and energy band gap of different CNTs

In order to study the effect of chirality on the performance of GAA-CNFET, the device was virtually fabricated using TCAD simulator and its performance was studied. Figure 5 (a) shows the transfer characteristics of GAA-CNFET using different CNTs (CNT (10, 0), CNT (13,0), CNT (16, 0), CNT (19, 0) and CNT (25, 0)). It is observed from the plot that for all types of CNTs, drain current increases sharply with increase in gate voltage beyond 0.4 V. It can also be depicted from the graph that as chirality of CNT increases, drain current also increases. Typically, the drain current for CNT (25, 0) and CNT (10, 0) are 33.483  $\mu$ A and 27.2743  $\mu$ A at V<sub>g</sub> = 0.7 V, respectively. Although there is high output drain current for CNT (25, 0), but it has less gate control after the V<sub>g</sub> of 0.2 V. Figure 5 (b) shows the output characteristics of GAA-CNFET using different chiral CNTs. It is observed from the plot that as drain voltage increases, CNT (10, 0) and CNT (13, 0) does not show any significant drain current. However, for other CNTs drain current increases with increase in drain voltage. The trend shows that as chiral vector increases drain current also increases.

Figure 5. Effect of chirality on GAA- CNFET (a) transfer characteristics (b) output characteristics at  $V_g$  and  $V_d$  of 0.3 V, respectively.

In order to further analyse the characteristics of GAA-CNFET, effect of chirality on subthreshold slope,  $I_{ON/OFF}$  ratio and transconductance is also studied using the device characteristics and parameters are extracted using Data Graph Digitizer software tool. In FET devices, high on/off ratio, subthreshold slope and transconductance are required for reducing the leakage current and high switching speed. These parameters with their values are listed in Table 2. It is clear from the table that there exists a tradeoff between the parameters for a given chiral CNT. For example, there is high  $I_{ON/OFF}$  ratio and less subthreshold slope for CNT (10, 0) and CNT (13, 0), however for these CNTs, device shows less transconductance value. CNFET with CNT (25, 0) has low  $I_{ON/OFF}$  ratio because of less gate control which leads to high subthreshold slope. For CNT (16, 0), CNFET has moderate current on/off ratio and subthreshold slope and CNFET with CNT (19, 0) has high transconductance, so both CNTs (16, 0) and (19, 0) are suitable for GAA-CNFET.

| CNT     | Subthreshold Slope<br>(mV/dec) | I <sub>ON</sub> /I <sub>OFF</sub> Ratio (×10 <sup>6</sup> ) | Transconductance (μS) |

|---------|--------------------------------|-------------------------------------------------------------|-----------------------|

| (10, 0) | 69.96                          | 70.406                                                      | 58.2621               |

| (13, 0) | 75.32                          | 77.823                                                      | 63.7227               |

| (16, 0) | 79.24                          | 24.693                                                      | 67.9316               |

| (19, 0) | 81.87                          | 0.6509                                                      | 71.0808               |

| (25, 0) | 86.55                          | 0.0115                                                      | 76.8234               |

**Table 2** Characteristic parameters of CNFET

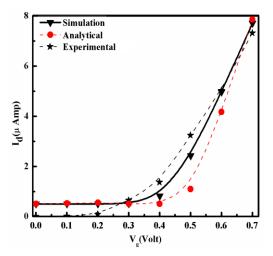

In order to check the validity of this simplified surface potential-based current model, we have compared the results obtained from simulation and analytical model with experimental results available in literature for fabricated GAA-CNFET [23]. Figure 6 shows the comparison of the transfer characteristics between experimental, simulation and analytical model for GAA-CNFET. The variation between the drain current versus gate voltage shows similar trend with the fabricated device. The small variation between experimental and analytical results may be attributed due to the fact that in fabricated device, an adhesion layer of  $\sim$ 1-nm AlO<sub>x</sub>N<sub>y</sub> is also used with 8 nm HfO<sub>2</sub> as a gate dielectric. Therefore, the close match between results confirms the validity of the proposed model.

Figure 6. Comparison between analytical results with simulation and experimental results [23]

## 4. CONCLUSION

We have proposed a surface-potential based model to investigate the performance of the GAA-CNFET in this paper. In the simplified surface-potential based model, the drain current depends on the surface potential of CNT. This model is based on the ballistic transportation of the charge carriers and neglect the screening and fringing effects. We also studied the effect of chirality on the device performance and it was found that CNT (16, 0) and (19, 0) shows average on/off ratio and high subthreshold slope and transconductance as compared to other chiral CNTs. Later, to validate the proposed model, results were compared with the experimental results of fabricated device using CNT (16, 0) as channel in CNFET. The close match between these two results confirms the validity of proposed model.

## ACKNOWLEDGEMENTS

Authors acknowledge the financial support of Defence Research and Development Organisation (DRDO), Govt. of India [ERIP/ER/DGMED&OS/990416502/M/01/1657] for carrying out research work reported this paper.

## REFERENCES

- [1] M. Najari, S. Fregonese, C. Maneux, H. Mnif, N. Masmoudi, T. Zimmer, IEEE Transactions on Electron Devices **58** (2011) 195–205.

- [2] F. Obite, G. Ijeomah, J. S. Bassi, International Journal of Computers and Applications **41** (2019) 149-164.

- [3] R. Hajare, Lakshminarayana, G. H. Raghunandan, C. P. Raj, Microsystem Technologies **22** (2016) 1121-1126.

- [4] H-S P. Wong et al., International Electron Devices Meeting, IEDM Tech. Dig. (2011), 23.1.1-23.1.4.

- [5] S. Garg, T. K. Gupta, Journal of Nanoelectronics and Optoelectronics, **14** (2019) 19-32.

- [6] D. J. Frank, R. H. Dennard, E. Nowak, P. M. Soloman, Y. Yaur, H-S P Wong, Proc. IEEE, **89**, (2001) 259-288.

- [7] L. Xu, C. Qiu, C. Zhao, Z. Zhang, L-M Peng, IEEE Transactions on Electron Devices, 66 (2019) 3535-3540.

- [8] A. Javey, J. Guo, Q. Wang, M. Lundstrom H. Dai, Nature, **424** (2003) 654-657.

- [9] K. Natori, Y. Kimura, T. Shimizu, J Appl. Phys., 97 (2005) 034306.

- [10] A. D. Franklin et. al, Nano Lett., 12 (2012) 758-762.

- [11] C. S. Lee, E Pop, A D Franklin, W Haensch, H-S P Wong, IEEE Transactions on Electron Devices, **62** (2015) 3061-3069.

- [12] P. Reena Monica, N. Chaubey, V. T. Sreedevi, Materials Today: Proceedings, 3 (2016) 2295– 2304.

- [13] M. H. Moaiyeri, F. Razi, Journal of Computational Electronics, 16 (2017) 240–252.

- [14] B. Jena, K. P. Pradhan, S. Dash, G. P. Mishra, P. K. Sahu, S. K. Mohapatra, Advances in Natural Sciences: Nanoscience and Nanotechnology, 6 (2015) 035010 (1-4).

- [15] S. Chaudhury, S. K, Sinha, Nanoelectronics (2019) 375–398.

- [16] R. Marani, R., A. G. Perri, International Journal of Electronics, 99, (2012) 437–444.

- [17] S. Datta, Quantum Transport: Atom to Transistor, Cambridge, U.K: Cambridge Univ. Press, 2006.

- [18] J. Guo, A. Javey, H Dai, M. Lundstrom, International Electron Devices Meeting IEDM Tech Dig. (2004) 703-706.

- [19] J. Luo et. al, IEEE Transactions on Electron Devices, **60** (2013) 1834-1843.

- [20] A. Dixit, N. Gupta, Journal of Micromechanics and Microengineering, 29 (2019) 094002 (1-6).

- [21] A. Raychowdhury, S. Mukhopadhyay, K. Roy, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, **23** (2004) 1411-1420.

- [22] I. O'Connor et al., IEEE Transactions on circuits and systems 54 (2007) 2365-2379.

- [23] A. D Franklin, S. O. Koswatta, D. Farmer, G. S. Tulevski, J. T. Smith, H. Miyazoe, W. Haensch, International Electron Devices Meeting, (2012) 4-5.

- [24] T. W. Odom, J. L. Huang, C. M. Lieber, J. Physics Chem. B, 104 (2000) 2794-2809.

- [25] H Kataura, Y Kumazawa, Y Maniwa, I Umeza, S Suzuki, Y Ohtsuka, Y Achiba, Synthetic Met., 103 (1999) 2555- 2558.

- [26] A. Dixit, N. Gupta, Bulletin of Electrical Engineering and Informatics, 9. (2020) 943-949.

- [27] A. Deyasi and A. Sarkar, International Journal of Electronics, 105, (2018): 2144-2159.

- [28] A. Dixit and N. Gupta, 2018 IEEE Electron Devices Kolkata Conference (EDKCON), Kolkata, India, (2018) 354-357

Ankita Dixit and Navneet Gupta / A Simplified Surface Potential Based Current Model ...

·